Jetzt ist Ihre Meinung gefragt zu 3D X-DRAM und VS-DRAM: Auch der Arbeitsspeicher soll gestapelt werden

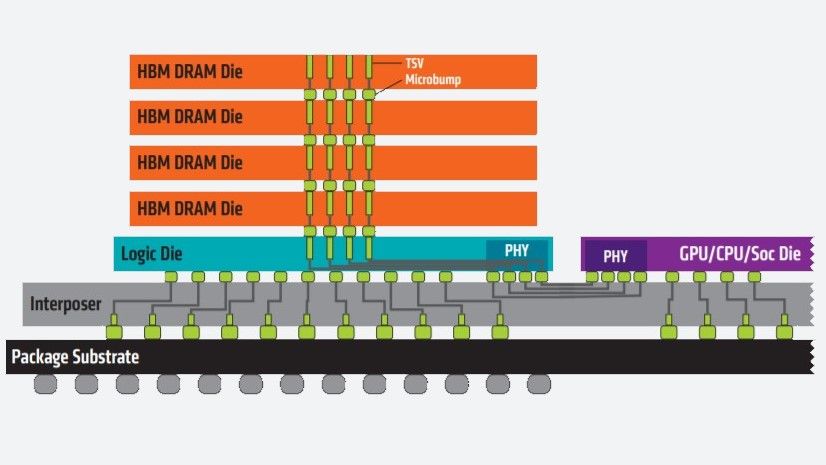

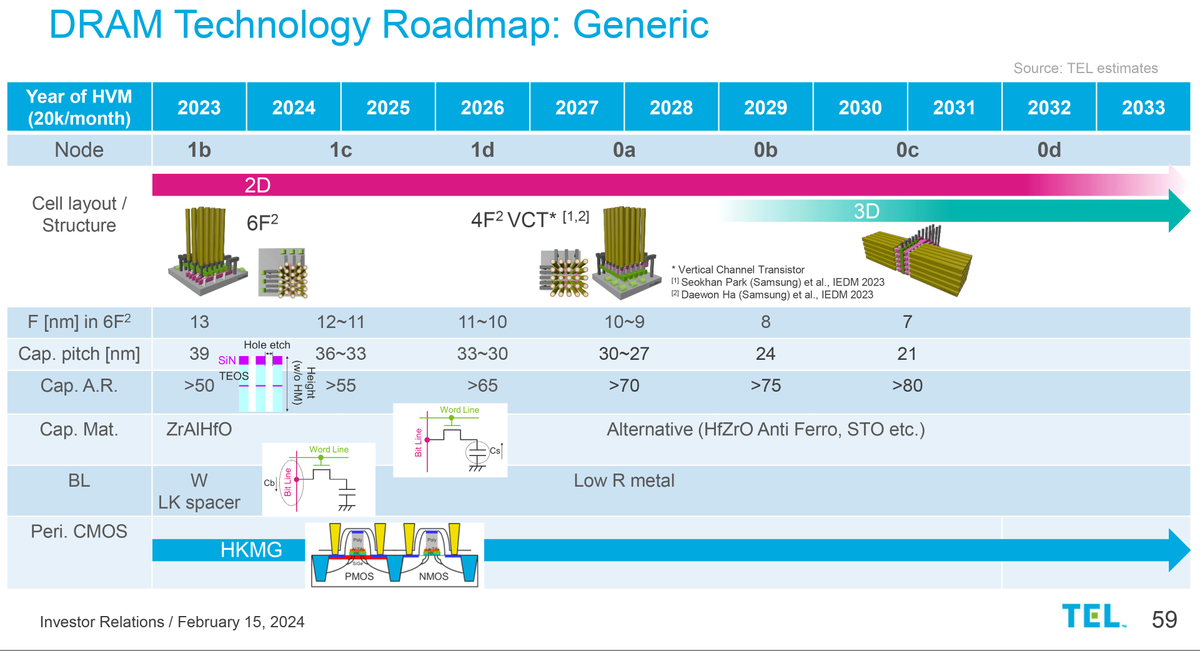

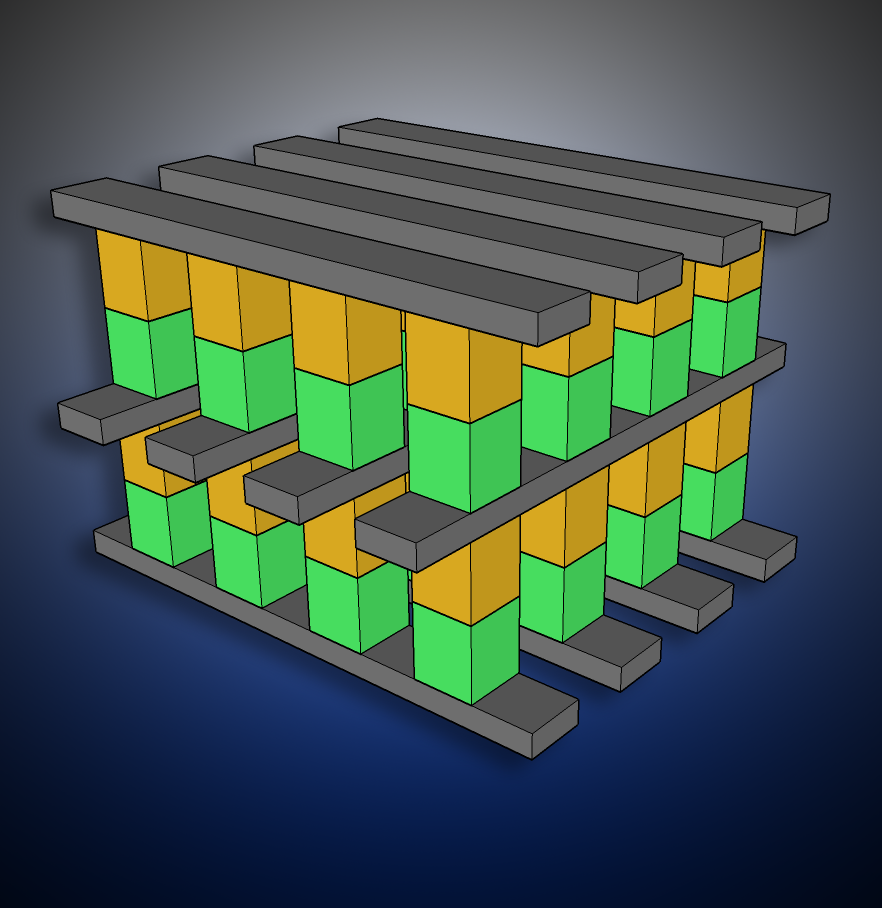

3D-NAND und 3D V-Cache sind mittlerweile den meisten Anwendern ein Begriff, aber in Zukunft sollen auch die DRAM-Speicherzellen für Arbeitsspeicher gestapelt werden. Während Samsung an VS-DRAM arbeitet, möchte das Start-up Neo Semiconductor seinen 3D X-DRAM etablieren. Ziel ist es, damit die Flächendichte deutlich steigern zu können.

Bitte beachten Sie: Der Kommentarbereich wird gemäß der Forenregeln moderiert. Allgemeine Fragen und Kritik zu Online-Artikeln von PC Games Hardware sind im Feedback-Unterforum zu veröffentlichen und nicht im Kommentarthread zu einer News. Dort werden sie ohne Nachfragen entfernt.

Zurück zum Artikel: 3D X-DRAM und VS-DRAM: Auch der Arbeitsspeicher soll gestapelt werden

3D-NAND und 3D V-Cache sind mittlerweile den meisten Anwendern ein Begriff, aber in Zukunft sollen auch die DRAM-Speicherzellen für Arbeitsspeicher gestapelt werden. Während Samsung an VS-DRAM arbeitet, möchte das Start-up Neo Semiconductor seinen 3D X-DRAM etablieren. Ziel ist es, damit die Flächendichte deutlich steigern zu können.

Bitte beachten Sie: Der Kommentarbereich wird gemäß der Forenregeln moderiert. Allgemeine Fragen und Kritik zu Online-Artikeln von PC Games Hardware sind im Feedback-Unterforum zu veröffentlichen und nicht im Kommentarthread zu einer News. Dort werden sie ohne Nachfragen entfernt.

Zurück zum Artikel: 3D X-DRAM und VS-DRAM: Auch der Arbeitsspeicher soll gestapelt werden

.gif)